### **Description**

The APO3105ASDNA Over-Voltage Protection device features a very low  $R_{\text{DS\_ON}}$  resistance, typical  $45m\Omega,$  internal nFET for USB VBUS line. The nFET switch ensures safe and right current flow in both charging and host modes such as OTG while protecting the internal system circuits from any over voltage conditions. Overvoltage threshold can be adjusted externally with a resistor divided network, or set internally by the built-in value.

The device features an open-drain output nACK, when  $V_{\text{IN\_UVLO}} < V_{\text{IN}} < V_{\text{IN\_OVLO}}$  and the switch is on, nACK will be driven low to indicate a good power input, otherwise it is high impedance.

This device features over-temperature protection that prevents itself from thermal damaging.

The APO3105ASDNA is available in a RoHS and Green compliant DFN2x2-6L package.

### **Applications**

- Mobile Handsets

- Tablets

- Wearable Devices

- Charging Ports

#### **Features**

- Fast OVP response with typical 60ns

- A low R<sub>DS ON</sub> 42mΩ (typ.) n-Channel MOSFET

- Very fast over voltage response with typical 60ns

- Adjustable OVP Threshold from 4V to 16V

- Default Threshold Voltage

- ♦ 6.0V for APO3105ASDNA

- VBUS DC Input Voltage Range : 2.8V ~ 32V

- VBUS Pulse Input Voltage Peak: <35V

- 4A Max Continuous Current Capability

- Enable function is active low

- No inrush current design

- OTG Functionality on VBUS Path

- Active-low Switch Status Indicator Output

- DFN2x2-6L package

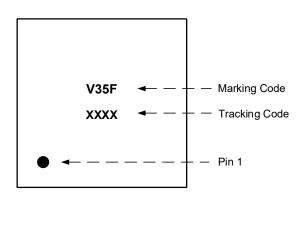

### **Device Comparison Table and Ordering Information**

| Part         | Package    | Operation Ambient<br>Temperature | Shipping Option  | Marking  | V <sub>IN_OVLO</sub> |

|--------------|------------|----------------------------------|------------------|----------|----------------------|

| APO3105ASDNA | DFN-2x2-6L | -40°C ~ 85°C                     | 3000/Tape & Reel | V35FXXXX | 6.0V                 |

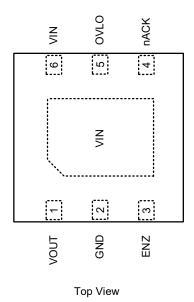

# **Pin Configuration and Top Mark**

Top Mark

# **Pin Assignments**

| Pin | Name             | Description                                                                                                                                                                                         |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>OUT</sub> | Output Voltage: bypass with a $0.1\mu F/35V$ ceramic capacitor as close to the device as possible. Capacitor breakdown voltage selected is depended on OVLO threshold set.                          |

| 2   | GND              | Ground                                                                                                                                                                                              |

| 3   | ENZ              | Enable pin: active low                                                                                                                                                                              |

| 4   | nACK             | Open-Drain Active-Low Output : Active-low logic output. It needs an external pull-up resistor, e.g. $10k\Omega \sim 470~k\Omega$ , to the System I/O. If not used, leave it open or tied to ground. |

| 5   | OVLO             | OVP Threshold Adjustment: Connect the pin to ground to use a fixed internal threshold. Connect a resistor-divider to set a different threshold between 4V and 16V.                                  |

| 6   | V <sub>IN</sub>  | Voltage Input: bypass with a 0.1µF/50V ceramic capacitor as close to the device as possible.                                                                                                        |

| EP  | V <sub>IN</sub>  | Voltage Input: Need to short to Pin 6 with wide metal trace.                                                                                                                                        |

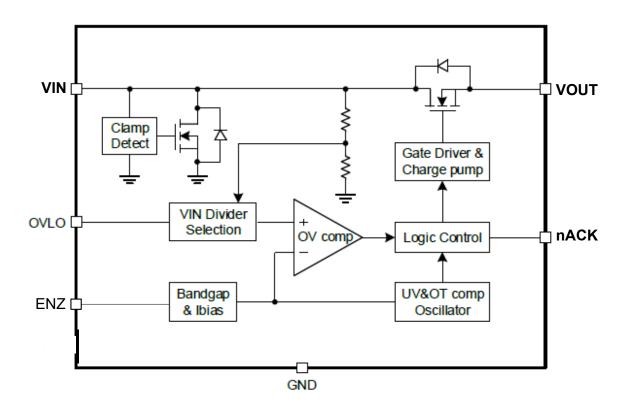

## **Functional Block Diagram**

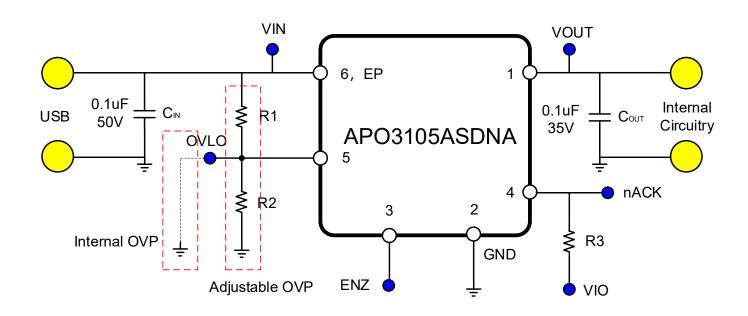

## **Typical Application Circuit**

# Absolute Maximum Ratings (T<sub>A</sub> = 25°C unless otherwise specified)

| Parameter                                    | Symbol            | Min  | Max | Unit |

|----------------------------------------------|-------------------|------|-----|------|

| Input DC voltage                             | V <sub>IN</sub>   | -0.3 | 35  | V    |

| Output voltage                               | V <sub>OUT</sub>  | -0.3 | 18  | V    |

| OVLO voltage                                 | V <sub>OVLO</sub> | -0.3 | 7   | V    |

| nACK voltage                                 | V <sub>ACK</sub>  | -0.3 | 7   | V    |

| ENZ voltage                                  | V <sub>ENZ</sub>  | -0.3 | 7   | V    |

| Switch current (Continuous current)          | I <sub>IN</sub>   |      | 4   | Α    |

| Ambient temperature                          | T <sub>A</sub>    | -20  | 85  | °C   |

| Junction temperature                         | TJ                | -40  | 125 | °C   |

| Storage temperature                          | T <sub>STG</sub>  | -55  | 150 | °C   |

| Soldering temperature (At leads, 10 seconds) | T <sub>LEAD</sub> |      | 260 | °C   |

# **Thermal Information**

| Parameter                                                 | Symbol           | Value | Unit |

|-----------------------------------------------------------|------------------|-------|------|

| Thermal resistance from junction to ambient (In free air) | R <sub>⊝JA</sub> | 70    | °C/W |

# **Operating Conditions**

| Parameter               | Symbol    | Min  | Max | Unit |

|-------------------------|-----------|------|-----|------|

| Input DC Voltage        | Vin       | 2.8  | 32  | V    |

| Input Capacitance       | CIN       | 0.1  |     | μF   |

| Output Load Capacitance | Соит      | 0.1  | 220 | μF   |

| Human Body Model        |           | -4   | 4   | kV   |

| Charged Device Model    | VESD      | -2   | 2   | kV   |

| Latch-up                | ILatch-up | -200 | 200 | mA   |

# Electrical Characteristics ( $V_{IN} = 5V$ , $T_A = 25$ °C unless otherwise specified)

| Parameter                               | Symbol          | Test Condition                     | Min | Тур | Max   | Unit |

|-----------------------------------------|-----------------|------------------------------------|-----|-----|-------|------|

| Switch on resistance                    | RDS_ON          | VIN = 5V, IOUT = 1A                |     | 42  | 55    | mΩ   |

| Switch on resistance                    | NDS_ON          | VIN = 3.3V, IOUT = 1A              |     | 49  | 10 μΑ | mΩ   |

| Shutdown current                        | I <sub>SD</sub> | V <sub>IN</sub> = 5V, ENZ floating |     | 5   | 10    | μA   |

| Input quiescent current                 | lq              | VIN = 5V, VOVLO = 0V, IOUT = 0A    |     | 115 | 145   | μA   |

| Input current at over-voltage condition | lin_ovlo        | VIN = 5V, VOVLO = 3V, VOUT = 0V    |     | 103 | 130   | μΑ   |

| LIVI O trip lovel                       | Vacando         | V <sub>IN</sub> rising             |     |     | 2.8   | V    |

| UVLO trip level                         | VIN_UVLO        | Vเง falling                        | 2.0 |     |       | V    |

| ENZ high input voltage                  | V <sub>IH</sub> |                                    | 1.2 |     |       | V    |

| ENZ low input voltage                   | V <sub>IL</sub> |                                    |     |     | 0.4   | V    |

# Electrical Characteristics (T<sub>A</sub> = 25°C unless otherwise specified)

| Parameter                       | Symbol           | Test Condition   | Min  | Тур  | Max       | Unit |  |  |

|---------------------------------|------------------|------------------|------|------|-----------|------|--|--|

| Protection                      |                  |                  |      |      |           |      |  |  |

| OVD tries level                 | \(\frac{1}{2} \) | Vin rising       |      | 6    |           |      |  |  |

| OVP trip level                  | VIN_OVLO         | Hysteresis       |      | 0.15 | 0.32<br>V | V    |  |  |

| External OVLO select threshold  | Vovlo_sel        | OVLO Rising      | 0.26 | 0.29 | 0.32      | V    |  |  |

|                                 | VOVLO_SEL        | Hysteresis       |      | 0.04 |           | V    |  |  |

| OVLO set threshold              | Vovlo_th         |                  | 1.16 | 1.20 | 1.24      | V    |  |  |

| OVP threshold adjustable range  | Vovlo_rn<br>g    |                  | 4    |      | 16        | V    |  |  |

| OVLO pin leakage current        | lovLo            | Vovlo = Vovlo_th | -0.1 |      | 0.1       | μA   |  |  |

| Shutdown temperature            | Tsdn             |                  |      | 140  |           | °C   |  |  |

| Shutdown temperature hysteresis | TSDN_HYS         |                  |      | 30   |           | °C   |  |  |

# Electrical Characteristics (T<sub>A</sub> = 25°C unless otherwise specified)

| Parameter              | Symbol       | Test Condition                                                                                                            | Min | Тур | Max | Unit |

|------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Timing Characteristics |              |                                                                                                                           |     |     |     |      |

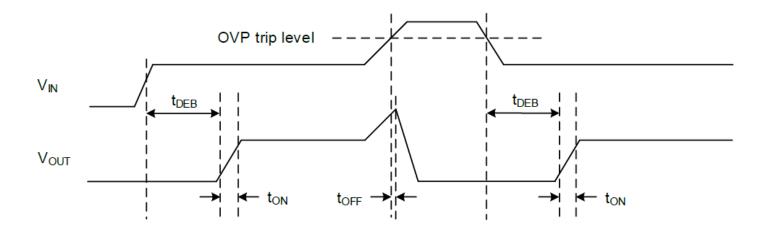

| Debounce time          | <b>t</b> DEB | From $V_{IN} > V_{IN\_UVLO}$ to 10% $V_{OUT}$                                                                             |     | 23  | 30  | ms   |

| Switch turn-on time    | ton          | $R_{OUT}$ = 100 $\Omega$ , $C_{OUT}$ = 0.1 $\mu$ F, $V_{OUT}$ from 10% $V_{IN}$ to 90% $V_{IN}$                           |     | 305 |     | μs   |

| Switch turn-off time   | toff         | $R_{OUT} = 100~\Omega, C_{OUT} = 0.1 \mu F, V_{IN} > \\ V_{IN\_UVLO}~to~V_{OUT}~stop~rising,~V_{IN}~rise \\ at~10V/\mu s$ |     | 60  |     | ns   |

# **Timing Diagram**

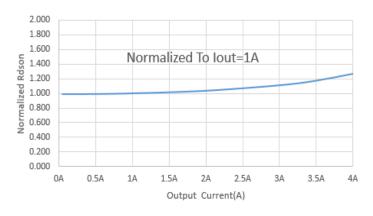

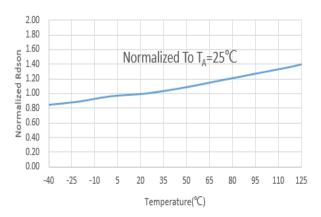

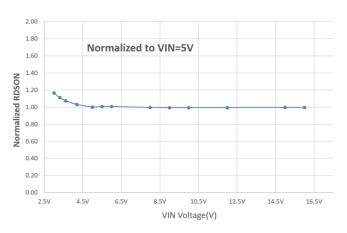

# Typical Performance Characteristics ( $V_{IN} = 5V$ , $C_{IN} = C_{OUT} = 0.1 \mu F$ , $T_A = 25 ^{\circ}C$ )

Normalized R<sub>DS ON</sub> vs Output Current. (V<sub>IN</sub>=5V)

Normalized R<sub>DS\_ON</sub> vs Temp. (I<sub>OUT</sub>=1A)

Normalized R<sub>DS\_ON</sub> vs Input Voltage (I<sub>OUT</sub>=1A)

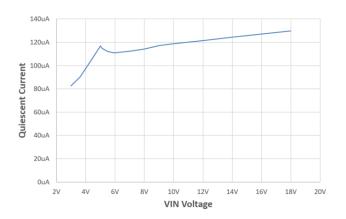

Input Supply Current vs Supply Voltage

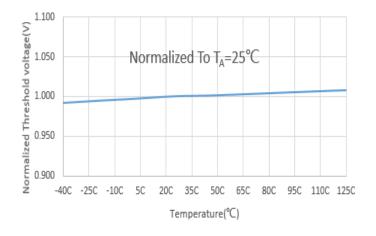

**Normalized Internal OVP Threshold**

Revision 1.0 8 of 14 www.appliedpowermicro.com

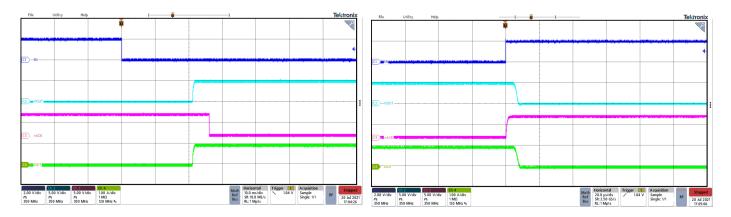

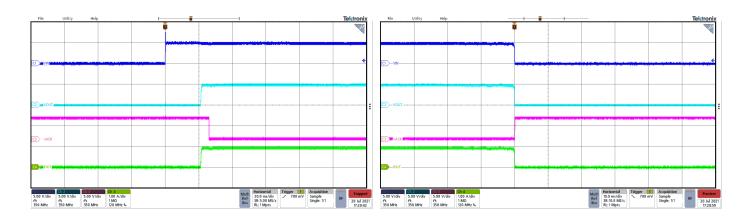

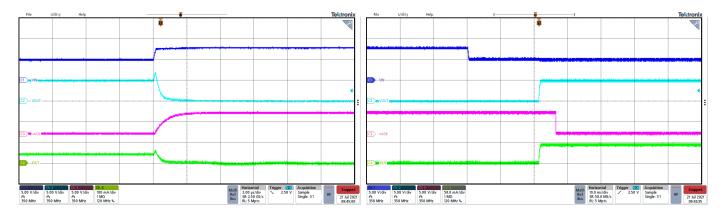

Typical Performance Characteristics (V<sub>IN</sub>= 5V, C<sub>IN</sub>= C<sub>OUT</sub>= 0.1  $\mu$ F, R<sub>OUT</sub> = 100 $\Omega$ , OVLO = GND T<sub>A</sub> = 25°C, V<sub>IO</sub>= 5V, R<sub>3</sub> = 47K $\Omega$ )

EN ON with  $5\Omega$  Load

EN OFF with  $5\Omega$  Load

Power on with  $5\Omega$  Load

Power off with  $5\Omega$  Load

**OVP Response**

**Recovery from OVP**

Revision\_1. 0 9 of 14 www.appliedpowermicro.com

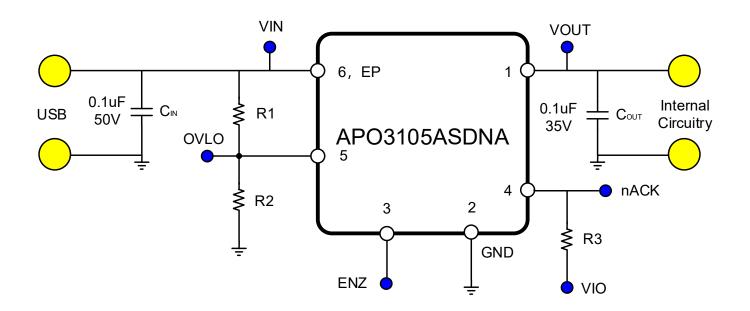

## **Typical Application circuit**

**Fixed OVP circuit**

**Adjustable OVP circuit**

Revision\_1. 0 10 of 14 www.appliedpowermicro.com

### **Functional Description**

#### **Device Operation**

If the input voltage is between UVLO and OVP threshold, the internal charge pump begins to work after debounce time, the gate of the nFET switch will be slowly charged high till the switch is fully on. If the input voltage exceeds the OVP trip level, the switch will be turned off in about 90ns. If input voltage falls below UVLO threshold, or over-temperature happens, the switch will also be turned off.

### **Over-Voltage Protection**

If the input voltage exceeds the OVP rising trip level, the switch will be turned off in typical 55ns. The switch will remain off until V<sub>IN</sub> falls below the OVP falling trip level.

### **OVP Threshold Adjustment**

If OVLO pin is not grounded, and by connecting external resistor divider to OVLO pin as shown in the typical application circuit, between IN and GND, the OVP threshold can be set as following formula:

$$V_{IN_OVLO} = (R_1+R_2) / R_2 * V_{OVLO_TH}$$

The adjustment range is 4V to 16V. When the OVLO pin voltage VovLo exceeds VovLo\_SEL (0.29V typical), VovLo is compared with the reference voltage VovLo TH (1.2V typical) to judge whether input supply is over-voltage.

#### **USB On-The-Go (OTG) Operation**

If  $V_{IN}$  = 0V and OUT is supplied by OTG voltage, the body diode of the load switch conducts current from OUT to IN and the voltage drop from OUT to IN is approximately 0.7V. When  $V_{IN}$  >  $V_{IN\_UVLO}$ , internal charge pump begins to open the load switch after debounce time. After switch is fully on, current is supplied through switch channel and the voltage drop from OUT to IN is minimum.

#### **Load Switch Status Indicator**

The device has a load switch status indicator to notify load switch on/off status to other devices. When load switch is on status, the device pulls nACK pin down to the GND. To avoid glitch during power up, it is recommended to limit rising slew rate at VIN less than 1V/uS or de-assert ENZ after power-up.

#### **Enable function**

The device has a enable pin that it is available with active low. When it is active high, the device will enter ECO mode with typical 2uA low standby current.

### **Thermal Protection**

The device has an Over-Temperature Protection circuit to protect device against system fault or improper use. When the junction temperature exceeds the threshold, 145°C typical, the device shuts down and stays off until the temperature cools down to a safe region (below falling threshold). Once the falling threshold, the device will automatically resume the normal operation with embedded timings.

# **Device Operation Summary**

| Conditio         | ns                | •                                                          |      |      |                  |

|------------------|-------------------|------------------------------------------------------------|------|------|------------------|

| V <sub>IN</sub>  | V <sub>OUT</sub>  | Current Direction                                          | nFET | nACK | Mode             |

| < OVP Threshold  | < V <sub>IN</sub> | $V_{IN} \rightarrow V_{OUT}$                               | On   | Low  | Charge           |

| < OVP Threshold  | > V <sub>IN</sub> | $V_{OUT} \rightarrow V_{IN}$                               | On   | Low  | OTG              |

| ≥ OVP Threshold  | < V <sub>IN</sub> | No Current flowing                                         | Off  | Hi-z | OVP              |

| ≥ OVP Threshold  | > V <sub>IN</sub> | $V_{OUT} \rightarrow V_{IN}$ (via the junction body diode) | Off  | Hi-z | OVP              |

| < UVLO Threshold | < V <sub>IN</sub> | No Current flowing                                         | Off  | Hi-z | UVLO             |

| Don't Care       | Don't Care        | No Current flowing                                         | Off  | Hi-z | Thermal Shutdown |

### **PCB Layout Consideration**

- 1. All the peripherals should be placed as close to the device as possible. Place the input capacitor  $C_{IN}$  on the top layer and close to  $V_{IN}$  pin, and place the output capacitor  $C_{OUT}$  on the top layer and close to  $V_{OUT}$  pin.

- 2. Exposed Pad (EP) connects to V<sub>IN</sub>, which is USB connector, and conducts large current during normal operation as well as surge protection. Route it out as straight, wide and short as possible. Also keep other traces away from it to minimize possible EMI coupling.

- GND pin 2 conducts large current during surge protection. Make sure no signal trace blocks the path for current flow.

- 4. Use rounded corners on the power trace to decrease EMI.

- 5. If  $R_1$  and  $R_2$  are used, route OVLO line as short as possible to reduce parasitic capacitance.

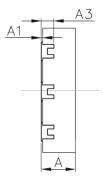

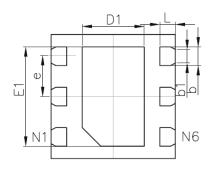

## **Package Outline Drawing**

TOP VIEW

SIDE VIEW

BOTTOM VIEW

| Symbol | Dimensions Ir | n Millimeters | Dimension  | s In Inches |  |

|--------|---------------|---------------|------------|-------------|--|

| Symbol | Min           | Max           | Min        | Max         |  |

| Α      | 0.700         | 0.800         | 0.028      | 0.031       |  |

| A1     | 0.000         | 0.050         | 0.000      | 0.002       |  |

| A3     | 0.203F        | REF.          | 0.008      | REF.        |  |

| D      | 1.900         | 2.100         | 0.075      | 0.083       |  |

| ш      | 1.900         | 2.100         | 0.075      | 0.083       |  |

| D1     | 0.900         | 1.100         | 0.035      | 0.043       |  |

| E1     | 1.500         | 1.700         | 0.059      | 0.067       |  |

| b      | 0.250         | 0.350         | 0.010      | 0.014       |  |

| b1     | 0.220         | REF.          | 0.009 REF. |             |  |

| е      | 0.650         | BSC.          | 0.026 BSC. |             |  |

| L      | 0.174         | 0.326         | 0.007      | 0.013       |  |

## **Contact Information**

Applied Power Microelectronics Inc.

Website: http://www.appliedpowermicro.com

Email: sales@appliedpowermicro.com

Phone: +86 (0519) 8399 3606

Applied Power Microelectronics Inc. (APM) reserves the right to make changes to the product specification and data in this document without notice. APM makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does APM assume any liability arising from the application or use of any products or circuits, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.