# 1.30 inch TFT Display Series

**GDTY0130H100N**

Dalian Good Display Co., Ltd.

## **Product Specifications**

| Customer    | Standard          |

|-------------|-------------------|

| Description | 1.30" TFT DISPLAY |

| Model Name  | GDTY0130H100N     |

| Date        | 2023/03/15        |

| Revision    | 1.0               |

| Design Engineering |      |        |  |  |

|--------------------|------|--------|--|--|

| Approval Check     |      | Design |  |  |

| 宝刘印玉               | 燕修印凤 | 之吴印良   |  |  |

No.18, Zhonghua West ST, Ganjingzi DST, Dalian, CHINA

Tel: +86-411-84619565

Email: info@good-display.com Website: www.good-display.com

## **CONTENTS**

| 1.General Specifications                        |

|-------------------------------------------------|

| 2.Mechanical Drawing 5                          |

| 3.PIN Assignment 6                              |

| 4. Absolute Maximum Rating                      |

| 5. Electrical Characteristics                   |

| 5.1.Recommended Operating Condition             |

| 5.2.Recommended Driving Condition for Backlight |

| 6.Timing Characteristics                        |

| 6.1.AC Electrical Characteristics               |

| 6.2. DC Electrical Characteristics              |

| 6.3.Power ON/OFF Sequence                       |

| 7.Optical Characteristics                       |

| 8. Environmental/Reliability Test               |

| 9. Standard Specifications For Product Quality  |

| 10. Precautions for Use of LCD Modules          |

## 1. General Specifications

| No | Item                | Contents         | Unit |

|----|---------------------|------------------|------|

| 1  | Size                | 1.3              | inch |

| 2  | Resolution          | 320*320          |      |

| 3  | Interface           | MIPI             |      |

| 4  | Technology Type     | a-Si TFT         |      |

| 5  | Sub pixel size      | 0.1035*0.1035    | mm   |

| 7  | Display Mode        | IPS,NB           |      |

| 8  | Viewing Direction   | ALL              |      |

| 9  | LCM (W x H x D)     | 36.12*38.85*1.24 | mm   |

| 10 | Active Area (W x H) | 33.12*33.12      | mm   |

| 11 | With/Without TSP    | Without TSP      |      |

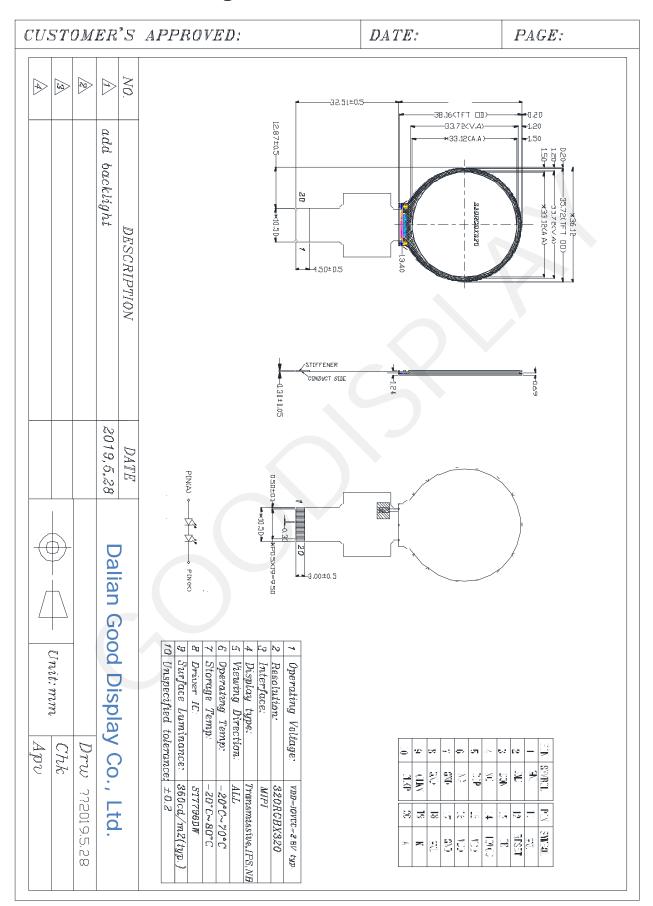

## 2. Mechanical Drawing

## 3. PIN Assignment

| Pin No | Symbol | I/O | Function                                                                                                        | Remark |

|--------|--------|-----|-----------------------------------------------------------------------------------------------------------------|--------|

| 1-2    | GND    | Р   | Ground                                                                                                          |        |

| 3      | D0N    | I/O | Negative polarity of low voltage differential clock signal                                                      |        |

| 4      | NC     | -   | No connection                                                                                                   |        |

| 5      | D0P    | I/O | Positive polarity of low voltage differential data signal.                                                      |        |

| 6      | NC     | -   | No connection                                                                                                   |        |

| 7-8    | GND    | Р   | Ground                                                                                                          |        |

| 9      | CLKN   | I   | Negative polarity of low voltage differential clock signal                                                      |        |

| 10     | CLKP   | IPo | sitive polarity of low voltage differential clock signal.                                                       |        |

| 11     | GND    | Р   | Ground                                                                                                          |        |

| 12     | RESET  | I   | This signal will reset the device and it must be applied to properly initialize the chip. Signal is active low. |        |

| 13     | TE     | 0   | Tearing effect output. If not used, leave this pin open.                                                        |        |

| 14     | IOVCC  | Р   | I/O power supply                                                                                                |        |

| 15-16  | VDD    | Р   | Power supply                                                                                                    |        |

| 17-18  | GND    | Р   | Ground                                                                                                          |        |

| 19     | K      | Р   | LED cathode                                                                                                     |        |

| 20     | Α      | Р   | LED anode                                                                                                       |        |

Ps: For further details, please refer to ST7796DW data sheet.

### 4. Absolute Maximum Rating

AGND = GND = 0V, Ta = 25°C

| Item                  | Symbol    | Min  | Max | Unit | Remark |

|-----------------------|-----------|------|-----|------|--------|

| Dawar Waltaga         | VDD       | -0.3 | 4.6 | V    |        |

| Power Voltage         | IOVCC     | -0.3 | 4.6 | V    |        |

| Operating Temperature | $T_{OPR}$ | -20  | 70  | ° C  |        |

| Storage Temperature   | $T_{STG}$ | -20  | 80  | ° C  |        |

The absolute maximum rating values of this product are not allowed to be exceeded at any times. Should a module be used with any of the absolute maximum ratings exceeded, the characteristics of the module may not be recovered, or in an extreme case, the module may be permanently destroyed.

### 5. Electrical Characteristics

### 5.1. Recommended Operating Condition

AGND = GND = 0V, Ta = 25°C

| Item                     | Symbol | Min      | Typ. | Max     | Unit | Remark |

|--------------------------|--------|----------|------|---------|------|--------|

| Dower Waltage            | VDD    | 2.5      | 2.8  | 3.3     | V    |        |

| Power Voltage            | IOVCC  | 1.65     | 2.8  | 3.3     | V    |        |

| Input logic high voltage | Vih    | 0.7 VDDI | -    | VDDI    | V    |        |

| Input logic low voltage  | VIL    | VSS      | -    | 0.3VDDI | V    |        |

## 5. 2. Recommended Driving Condition for Backlight

Ta = 25°C

|                     | _      |       |      |     |       |        |

|---------------------|--------|-------|------|-----|-------|--------|

| Item                | Symbol | Min   | Тур. | Max | Unit  | Remark |

| Forward Voltage     | Vf     | 5.8   |      | 6.6 | V     |        |

| Forward Current     | If     |       | 20   |     | mA    |        |

| Operating Life Time | -      | 20000 |      |     | Hours |        |

Note 1:The LED supply voltage is defined by the number of LED at  $Ta=25^{\circ}$  and If =20mA.

Note 2:The "Operating Life Time" is defined as the module brightness decrease to 50% original brightness at  $Ta=25\,^{\circ}\!\!\!$  and If = 20 mA. The LED lifetime could be decreased if operating If is larger than 20 mA.

## 6. Timing Characteristics

### 6.1. DC Electrical Characteristics

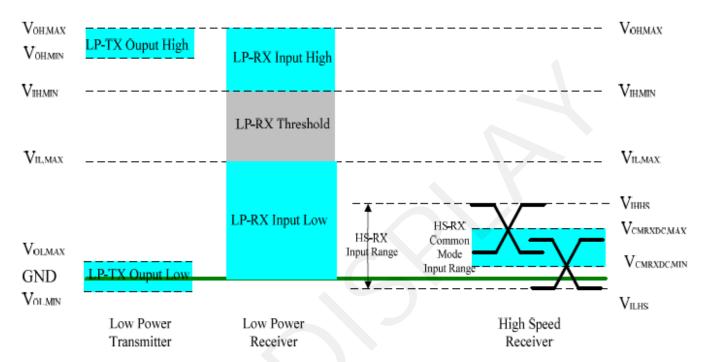

MIPI Signaling Voltage Levels

### MIPI DC characteristics

|                                              | Complete           |             | Specification | 1    |      |  |  |  |

|----------------------------------------------|--------------------|-------------|---------------|------|------|--|--|--|

| Parameter                                    | Symbol             | MIN         | TYP           | MAX  | Unit |  |  |  |

| Operati                                      | on Voltage for M   | IPI Receive | er            |      |      |  |  |  |

| Low power mode operating voltage             | VLPH               | 1.1         | 1.2           | 1.3  | ٧    |  |  |  |

| MIPI Characteristics for High Speed Receiver |                    |             |               |      |      |  |  |  |

| Single-ended input low voltage               | V ILHS             | -40         | -             | -    | mV   |  |  |  |

| Single-ended input high voltage              | V IHHS             | -           | -             | 460  | mV   |  |  |  |

| Common-mode voltage                          | VCMRXDC            | 70          | -             | 330  | mV   |  |  |  |

| Differential input impedance                 | Z ID               | 80          | 100           | 125  | ohm  |  |  |  |

| MIPI Char                                    | acteristics for Lo | w Power M   | lode          |      | '    |  |  |  |

| Pad signal voltage range                     | VI                 | -5          |               | 1350 | mV   |  |  |  |

|                                              | VI                 | 0           | -             | 1350 | mv   |  |  |  |

| Logic 0 input threshold                      | VIL                | 0           | -             | 550  | mV   |  |  |  |

| Logic 1 input threshold                      | 2011               | 88          |               |      | .,   |  |  |  |

|                                              | VIH                | 0           | -             | -    | mV   |  |  |  |

| Output low level                             | 1/01               | -5          |               |      | >    |  |  |  |

|                                              | VOL                | 0           | -             | 50   | mV   |  |  |  |

| Output high level                            | VOH                | 1.1         | 1.2           | 1.3  | ٧    |  |  |  |

## DC Characteristics for Panel Driving

| 72: 10                                                                                                     | 2 2 2         | The Mari                 | S           | pecificati | on      | 144. 21 | Related                |  |

|------------------------------------------------------------------------------------------------------------|---------------|--------------------------|-------------|------------|---------|---------|------------------------|--|

| Parameter                                                                                                  | Symbol        | Condition                | MIN.        | TYP.       | MAX.    | Unit    | Pins                   |  |

|                                                                                                            |               | Power & Operati          | ion Voltage |            |         |         | 9,                     |  |

| System Voltage                                                                                             | VDD /<br>VDDA | Operating voltage        | 2.5         | 2.8        | 3.3     | V       | (=:                    |  |

| Interface Operation Voltage                                                                                | VDDI          | I/O Supply<br>Voltage    | 1.65        | 2.8        | 3.3     | V       | re.                    |  |

| Gate Driver High Voltage                                                                                   | VGH           | R <del>e</del> s         | 12.6        | 241        | 15.5    | V       | -                      |  |

| Gate Driver Low Voltage                                                                                    | VGL           | g <del>=</del> s         | -11.8       | 552        | -8.3    | V       | -                      |  |

| Gate Driver Supply Voltage                                                                                 | -             | VGH-VGL                  | =           | (4)        | 27.3    | V       | LET                    |  |

| 79 W. A. C. 1990, Br. 1991, G. C. C. 1990 B. G. C. C. C. C. 1990 B. C. |               | Input / Ou               | itput       |            |         |         | 2                      |  |

| Logic-High Input Voltage                                                                                   | VIH           | 12                       | 0.7VDDI     | 523        | VDDI    | V       | Note 1                 |  |

| Logic-Low Input Voltage                                                                                    | VIL           | y=-                      | VSS         | S#1        | 0.3VDDI | ٧       | Note 1                 |  |

| Differential Input High<br>Threshold Voltage                                                               | VIT+          | -                        |             | 0          | 50      | mV      |                        |  |

| Differential Input Low<br>Threshold Voltage                                                                | VIT-          | -                        | -50         | 0          | -       | mV      | MIPI_CLK,<br>MIPI_DATA |  |

| Single-ended Receiver Input<br>Operation Voltage Range                                                     | VIR           | -                        | 0.5         | -          | 1.2     | V       |                        |  |

| Logic-High Output Voltage                                                                                  | VOH           | IOH = -1.0mA             | 0.8VDDI     | -          | VDDI    | V       | Note 1                 |  |

| Logic-Low Output Voltage                                                                                   | VOL           | IOL = +1.0mA             | VSS         | -          | 0.2VDDI | V       | Note 1                 |  |

| Logic-High Input Current                                                                                   | IIH           | VIN = VDDI               | -           | -          | 1       | uA      | Note 1                 |  |

| Logic-Low Input Current                                                                                    | IIL           | VIN = VSS                | -1          | -          | -       | uA      | Note 1                 |  |

| Input Leakage Current                                                                                      | ILI           | IOH = -1.0mA             | -0.1        | -          | +0.1    | uA      | Note 1                 |  |

|                                                                                                            |               | VCOM Vo                  | ltage       |            |         |         |                        |  |

| VCOM Voltage                                                                                               | VCOM          | -                        | -           | VSS        | -       | V       | -                      |  |

|                                                                                                            |               | Source D                 | river       |            |         |         |                        |  |

| Gamma Reference<br>Voltage(Positive)                                                                       | VAP           | -                        | 4.45        | -          | 6.4     | ٧       | -                      |  |

| Gamma Reference<br>Voltage(Negative)                                                                       | VAN           | -                        | -4.6        | -          | -2.65   | -       | -                      |  |

| Source Output Settling Time                                                                                | Tr            | Below with 99% precision | -           | -          | 20      | us      | Note 2                 |  |

| Output Offset Voltage                                                                                      | VOFFSET       |                          | -           | -          | 35      | mV      | Note 3                 |  |

Basic DC Characteristics

Notes:

<sup>2.</sup> The max. value is between measured point of source output and gamma setting value.

## 6.2. Timing

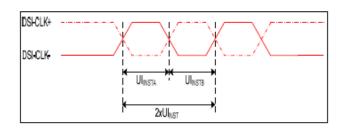

## High Speed Mode

### Clock Channel Timing

### Timing Characteristics

| Signal     | Symbol                                     | Parameter                | MIN  | MAX  | Unit | Description                                       |

|------------|--------------------------------------------|--------------------------|------|------|------|---------------------------------------------------|

| DSI-CLK+/- | 2xUIINSTA                                  | Double UI instantaneous  | 4    | 25   | ns   | -                                                 |

| DSI-CLK+/- | UI <sub>INSTA</sub><br>UI <sub>INSTB</sub> | UI instantaneous halfs   | 2    | 12.5 | ns   | UI = UI <sub>INSTA</sub> =<br>UI <sub>INSTB</sub> |

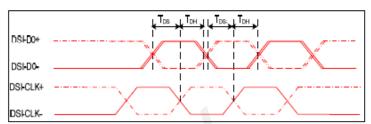

| DSI-Dn+/-  | tDS                                        | Data to clock setup time | 0.15 | -    | UI   | -                                                 |

| DSI-Dn+/-  | tDH                                        | Data to clock hold time  | 0.15 | -    | UI   | -                                                 |

### Data Transmission

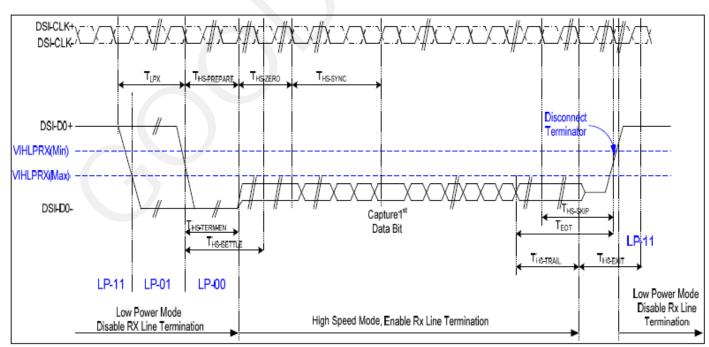

Data lanes-Low Power Mode to/from High Speed Mode Timing

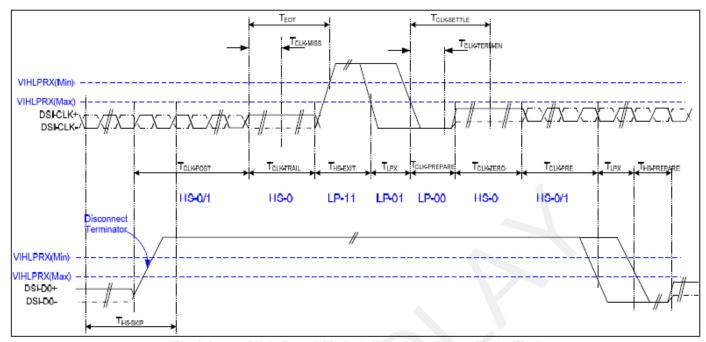

Clock lanes- High Speed Mode to/from Low Power Mode Timing

| Signal     | Symbol                      | Parameter                                                                                                                        | MIN         | MAX            | Unit  | Description |

|------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-------|-------------|

|            | Low                         | Power Mode to High Speed Mo                                                                                                      | de Timing   |                | ·     |             |

| DSI-Dn+/-  | TLPX                        | Length of any low power state period                                                                                             | 50          | -              | ns    | Input       |

| DSI-Dn+/-  | THS-PREPARE                 | Time to drive LP-00 to prepare for HS transmission                                                                               | 40+4UI      | 85+6L          | JI ns | Input       |

| DSI-Dn+/-  | THS-TERM-EN                 | Time to enable data receiver<br>line termination measured<br>from<br>when Dn crosses VILMAX                                      | -           | 35+40          | JI ns | Input       |

| DSI-Dn+/-  | THS-PREPARE                 | THS-PREPARE + time to drive HS-0 before the sync                                                                                 | 140+10U     | J .            | ns    | Input       |

|            | + THS-ZERO                  | sequence                                                                                                                         |             |                |       |             |

|            | Higl                        | h Speed Mode to Low Power Mo                                                                                                     | de Timing   |                |       |             |

| DSI-Dn+/-  | THS-SKIP                    | Time-out at display module to ignore transition period of EoT                                                                    | 40          | 55+4UI         | ns    | Input       |

| DSI-Dn+/-  | THS-EXIT                    | Time to drive LP-11 after HS burst                                                                                               | 100         | -              | ns    | Input       |

| DSI-Dn+/-  | THS-TRAIL                   | Time to drive flipped differential state after last payload data bit of a HS transmission burst                                  | 60+4UI      | -              | ns    | Input       |

|            | High S                      | Speed Mode to/from Low Power I                                                                                                   | Mode Timi   | ng             | 1     |             |

| DSI-CLK+/- | TCLK-POS                    | Time that the MPU shall continue sending HS clock after the last associated data lane has transition to LP mode                  | 60+52<br>UI | -              | ns    | Input       |

| DSI-CLK+/- | TCLK-TRAIL                  | Time to drive HS differential state after last payload clock bit of a HS transmission burst                                      | 60          | -              | ns    | Input       |

| DSI-CLK+/- | THS-EXIT                    | Time to drive LP-11 after HS burst                                                                                               | 100         | -              | ns    | Input       |

| DSI-CLK+/- | TCLK-PREPARE                | Time to drive LP-00 to<br>prepare<br>for HS transmission                                                                         | 38          | 95             | ns    | Input       |

| DSI-CLK+/- | TCLK-TERM-EN                | Time-out at clock lan display module to enable HS transmission                                                                   |             | 38             | ns    | Input       |

| DSI-CLK+/- | TCLK-PREPARE<br>+ TCLK-ZERO | Minimum lead HS-0 drive period before starting clock                                                                             | 300         | -              | ns    | Input       |

| DSI-CLK+/- | TCLK-PRE                    | Time that the HS clock shall<br>be<br>driven prior to any associated<br>data lane beginning the<br>transition from LP to HS mode | 8UI         | -              | ns    | Input       |

| DSI-CLK+/- | ТЕОТ                        | Time form start of<br>TCLK-TRAIL period to start of<br>LP-11 state                                                               | -           | 105ns+<br>12UI | ns    | Input       |

Mipi Interface- High Speed Mode Timing Characteristics

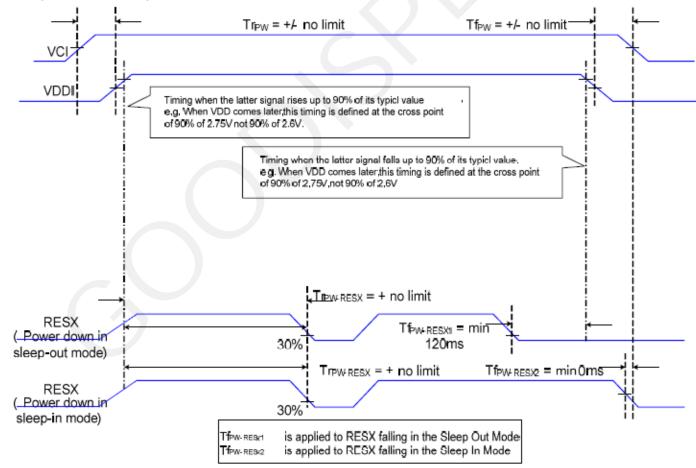

### 6. 3. Power ON/OFF Sequence

VDDI and VCI can be applied in any order.

VCI and VDDI can be power down in any order.

During power off, if LCD is in the Sleep Out mode, VCI and VDDI must be powered down minimum 120msec after RESX has been released.

During power off, if LCD is in the Sleep In mode, VDDI or VCI can be powered down minimum 0msec after RESX has been released.

- Note 1: There will be no damage to the display module if the power sequences are not met.

- Note 2: There will be no abnormal visible effects on the display panel during the Power On/Off Sequences.

- Note 3: There will be no abnormal visible effects on the display between end of Power On Sequence and before receiving Sleep Out command. Also between receiving Sleep In command and Power Off Sequence.

- Note 4: If RESX line is not held stable by host during Power On Sequence as defined in the sequence below, then it will be necessary to apply a Hardware Reset (RESX) after Host Power On Sequence is complete to ensure correct operation. Otherwise function is not guaranteed.

The power on/off sequence is illustrated below

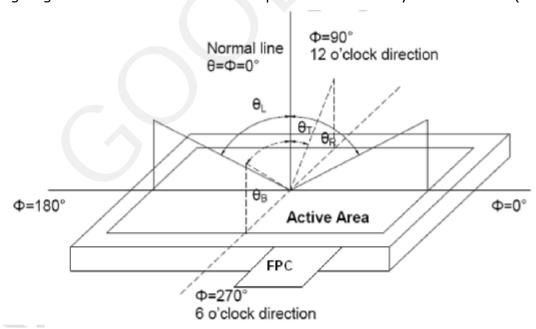

## 7. Optical Characteristics

| Item           | Symbol    | Condition            | Min | Тур  | Max | Unit              | Remark |

|----------------|-----------|----------------------|-----|------|-----|-------------------|--------|

|                | θТ        |                      | 45  | 60   |     |                   |        |

| 17: A1         | θВ        | CD > 10              | 45  | 60   |     | D                 | N-4- 2 |

| View Angles    | θГ        | CR≥10                | 45  | 60   |     | Degree            | Note 2 |

|                | θR        |                      | 45  | 60   |     |                   |        |

| Contrast Ratio | CR        | $\theta = 0^{\circ}$ | 900 | 1100 |     |                   | Note 1 |

| Contrast Ratio | CK        | · - 0                | 900 | 1100 | ,   |                   | Note 3 |

| Dagnanga Tima  | $T_{ON}$  | 25° C                | -   | 35   | 40  | 120 G             | Note 1 |

| Response Time  | $T_{OFF}$ | 25° C                |     |      |     | ms                | Note 4 |

| Luminance      | L         |                      |     | 260  |     | cd/m <sup>2</sup> | Note 1 |

| Lummance       | L         |                      |     | 360  |     | cu/m              | Note 5 |

### Test Conditions:

- 1. VDD=2.8V, the ambient temperature is 25°C.

- 2. The test systems refer to Note 2.

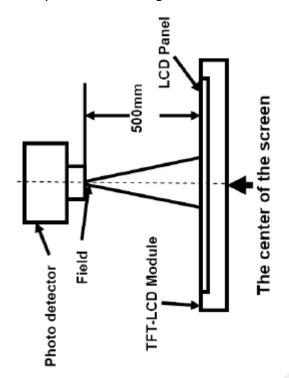

Note1: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 5Minutes operation, the optical properties are measured at the center point of the LCD screen. ALL input terminals LCD panel must be ground when measuring the center area of the panel.

| Item           | Photo detector | Field |  |

|----------------|----------------|-------|--|

| Contrast Ratio | 651000         |       |  |

| Luminance      | CS1000         | 10    |  |

| Lum Uniformity |                |       |  |

| Chromaticity   | CS1000         |       |  |

| Response Time  | DMS703         |       |  |

|                |                | -     |  |

Note2: Definition of viewing angle range and measurement system. Viewing angle is measured at the center point of the LCD by CONOSCOPE (DMS703)

Note3: Definition of contrast ratio

## Contrast ratio (CR) = Luminance measured when LCD is on the "White" state Luminance measured when LCD is on the "Black" state

"White state ": The state is that the LCD should drive by Vwhite.

"Black state ": The state is that the LCD should drive by Vblack.

Vwhite: To be determined Vblack: To be determined

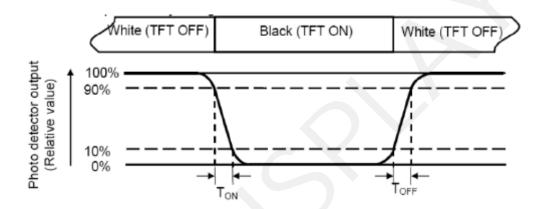

Note4: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White"state and "Black" state. Rise time (TON)is the time between photo detector output intensity changed from 90% to 10%. And fall time (TOFF)is the time between photo detector output intensity changed from 10% to 90%.

Note5:Definition of color chromaticity (CIE1931) Color coordinates measured at center point of LCD.

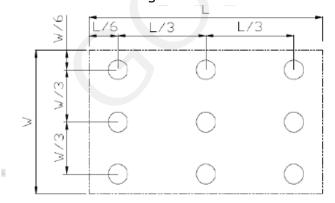

Note6: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas(Refer Fig.2). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U)=Lmin/Lmax

L-----Active area length W-----Active area width

L max: The measured Maximum luminance of all measurement position.

L min: The measured Minimum luminance of all measurement position.

Note7: Definition of luminance: Measure the luminance of white state at center point.

### 8. Environmental/Reliability Test

| No. | Test Item                     | Test Condition                                                                                     | Inspection after test                                     |

|-----|-------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 1   | High Temperature Storage      | 80±2°C/240 hours                                                                                   |                                                           |

| 2   | Low Temperature Storage       | -30 <b>±</b> 2℃/240 hours                                                                          | Inspection after                                          |

| 3   | High Temperature<br>Operating | 70±2℃/240 hours                                                                                    | 2~4hours storage at room temperature, the sample shall be |

| 4   | Low Temperature<br>Operating  | -20±2℃/240 hours                                                                                   | free from defects:                                        |

|     |                               | -30℃~25℃~80℃                                                                                       | 1.Air bubble in the LCD;                                  |

| 5   | Temperature Cycle             | ×10cycles<br>(30min.) (5min.)<br>(30min.)                                                          | 2.Sealleak; 3.Non-display; 4.missing segments;            |

| 6   | Damp Proof Test               | 60℃±5℃×90%RH/120 hours                                                                             | 5.Glass crack;                                            |

| 7   | Vibration Test                | Frequency: 10Hz~55Hz~10Hz Amplitude: 1.5mm, X, Y, Z direction for total 3hours (Packing condition) | 6.Current Idd is twice higher than initial value.         |

| 8   | Dropping test                 | Drop to the ground from 1m height, one time, every side of carton.  (Packing condition)            |                                                           |

| 9   | ESD test                      | Voltage:±8KV R: 330Ω C:<br>150pF<br>Air discharge, 10time                                          |                                                           |

|     |                               | Voltage:±6KV R: 330Ω<br>C: 150pF<br>Contact discharge, 10time                                      |                                                           |

### Remark:

- 1. The test samples should be applied to only one test item.

- 2. Sample size for each test item is 5~10pcs.

- 3.For Damp Proof Test, Pure water(Resistance>10M $\Omega$ ) should be used.

- 4.In case of malfunction defect caused by ESD damage, if it would be recovered to normal state after resetting, it would be judge as a good part.

- 5. Failure Judgment Criterion: Basic Specification, Electrical Characteristic, Mechanical Characteristic, Optical Characteristic.

- 6.Please use automatic switch menu(or roll menu) testing mode when test operating mode.

### 9. Standard Specifications For Product Quality

### 9.1. Manner of test:

10.1.1 The test must be under 40W fluorescent light, and the distance of view must be at  $30\pm10$ cm.

10.1.2 Room temperature 25±5°C Humidity: (60±10)%RH.

### 9.2. Quality specification

It shall be based on GB2828-87, inspection level II .

|       | IETM                                              | CHECK | LEVEL | AQL  |

|-------|---------------------------------------------------|-------|-------|------|

|       | 1.Liquid crystal leakage                          |       |       |      |

|       | 2. Wrong polarizer                                |       |       |      |

| MAJOR | 3.Outside dimension                               | II    |       | 0.25 |

| (MA)  | 4. Bright dot Dark dot                            | 11    |       | 0.23 |

|       | 5. Display abnormal                               |       |       |      |

|       | 6. Class crack                                    |       |       |      |

|       | 1. Spot Defect (Including black spot, white spot, |       |       |      |

|       | pinhole, foreign particle, bubbles, hurt)         |       |       |      |

|       | 2. fragment                                       |       |       |      |

| MINOR | 3. Line Defect (Including black line, white line, | II    |       | 1.0  |

| (MI)  | cratch)                                           | 11    |       | 1.0  |

|       | 4. Incision defect                                |       |       |      |

|       | 5. Newton's ring                                  |       |       |      |

|       | 6. Other visual defects                           |       |       |      |

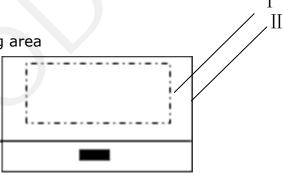

### 9.3. Definition of area:

10.3.1 I area: viewing area

II area: outside viewing area

## 9.4. Standard of appearance test for I area: (unit: mm)

NOTE: Defect ignore for II area .

## 9.4.1 Bright/Dark Dots explain

| Name             | Explain                                                                                                      | Definition                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Bright dot       | Dots appear bright and unchanged in size in which LCD panel is displaying under black pattern                | The definition of dot: The size of a defective dot over 1/2 of single                                                                           |

| Dark dot         | Dots appear dark and unchanged in size in which LCD panel is displaying under pure red, green, blue pattern. | pixel dot is regarded<br>as one defective dot.<br>NOTE: One pixel<br>consists of 3 sub-pixels,<br>including R,G, and B<br>dot.(Sub-pixel = Dot) |

| ADJACE<br>NT DOT | Adjacent two sub-pixel are defect (define two dot defect)                                                    |                                                                                                                                                 |

## 9.4.2 Inspection standard

| № | Items                                                                  | Criterion             |                                                                                                                                                                                                                                                                | Checking<br>Manner | Defect<br>Classes |

|---|------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|

|   |                                                                        | Under 6" (contain 6") | Bright dot: 2 Dark dot: N≤4 Note: be more than 5mm apart                                                                                                                                                                                                       |                    |                   |

| 1 | Bright/dark dot                                                        | 6"-12"                | Bright dot: N≤4 Dark dot: N≤5 Total Bright and Dark Dots: N≤8 Note: 1.Two bright dot defects (red, green, blue, and white) should be larger than 15mm; 2.The distance between black dot defects or black and bright dot defects should be more than 5mm apart. | Checking with eyes | MAJ               |

|   | Spot Defect<br>(Including black<br>spot.white spot.<br>Pinhole.foreign | Under 6" (contain 6") | D≤0.1 Ignore<br>0.1 < D≤0.35 N≤3<br>0.35 < D N=0                                                                                                                                                                                                               |                    |                   |

| 2 | particle.bubbles.h<br>urt)  X D=(X+Y)/2                                | 6"-12"                | D≤0.3 Ignore<br>0.3 < D≤0.6 N≤4<br>0.6 < D N=0                                                                                                                                                                                                                 | Checking with eyes | MIN               |

| №                                                      | Items             |                                                                                                    | Checking manner                                                     | Defect<br>classes  |     |

|--------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------|-----|

| Line Defect (Including black Line.white line. scratch) |                   | g black Under 6" $0.02 < W \le 0.04$ L $\le 5$ N $\le 2$                                           |                                                                     | Checking           |     |

| 3                                                      | L W               | 6"-12"                                                                                             | W≤0.07 Ignore<br>0.07 <w≤0.1 l≤10="" n≤4<br="">W&gt;0.1 N=0</w≤0.1> | with eyes          | MIN |

| 4                                                      | Display abnormal  | Not allowed                                                                                        |                                                                     | Checking with eyes | MAJ |

| 5                                                      | Outside dimension | Accord with dra                                                                                    | wing                                                                | Callipers          | MAJ |

| 6                                                      | Class crack       | Not allowed                                                                                        |                                                                     | Checking with eyes | MAJ |

| 7                                                      | Leak              | Not allowed                                                                                        | Checking with eyes                                                  | MAJ                |     |

| 8                                                      | Comer fragment    | X≤3 Y≤3 Z≤<br>Note:<br>1.No hurt identification 1.No hurt identification 2.T: Glass thic thickness | Checking with eyes                                                  | MIN                |     |

|                                                        | Side fragment     | Y≤1 Z≤T Ig<br>Note:<br>1.No hurt identif<br>2.T: Glass thic<br>thickness                           | Checking with eyes                                                  | MIN                |     |

| 9                                                      | Step fragment     | $Y \le 1$ and $Y \le 1/$                                                                           | Checking with eyes                                                  | MIN                |     |

|                                                        | Incision defect   | Y≤1 and accord                                                                                     | Checking with eyes                                                  | MIN                |     |

| №  | Items                                           |                              | Criterion                                                                                                                                              | Checking manner    | Defect<br>classes |

|----|-------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|

| 10 | Newton's ring (CTP or Cover board)  X D=(X+Y)/2 | Under 6" (contain 6") 6"-12" | D\(\leq 25  \text{N}\leq 3 \\ \text{D}\(\rightarrow 25  \text{N}=0 \)  \[ \text{D}\(\leq 70  \text{N}\leq 5 \\ \text{D}\(\rightarrow 70  \text{N}=0 \) | Checking with eyes | MIN               |

## 10. Precautions for Use of LCD Modules

### 10.1 Handing Precautions

- (1) The display panel is made of glass and polarizer. As glass is fragile. It tends to become or chipped during handling especially on the edges. Please avoid dropping or jarring. Do not subject it to a mechanical shock by dropping it or impact.

- (2) If the display panel is damaged and the liquid crystal substance leaks out, be sure not to get any in your mouth. If the substance contacts your skin or clothes, wash it off using soap and water.

- (3) Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary. Do not touch the display with bare hands. This will stain the display area and degraded insulation between terminals (some cosmetics are determined to the polarizer).

- (4) The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully. Do not touch, push or rub the exposed polarizers with anything harder than an HB pencil lead (glass,tweezers, etc.). Do not put or attach anything on the display area to avoid leaving marks on. Condensation on the surface and contact with terminals due to cold will damage, stain or dirty the polarizer. After products are tested at low temperature they must be warmed up in a container before coming is contacting with room temperature air.

- (5) If the display surface becomes contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If it is heavily contaminated, moisten cloth with one of the following solvents

- Isopropyl alcohol

- Ethyl alcohol

Do not scrub hard to avoid damaging the display surface.

- (6) Solvents other than those above-mentioned may damage the polarizer. Especially, do not use the following.

- Water

- Ketone

- Aromatic solvents

Wipe off saliva or water drops immediately, contact with water over a long period of time may cause deformation or color fading. Avoid contacting oil and fats.

- (7) Exercise care to minimize corrosion of the electrode. Corrosion of the electrodes is accelerated by water droplets, moisture condensation or a current flow in a high-humidity environment.

- (8) Install the LCD Module by using the mounting holes. When mounting the LCD module make sure it is free of twisting, warping and distortion. In particular, do not forcibly pull or bend the I O cable or the backlight cable.

- (9) Do not attempt to disassemble or process the LCD module.

- (10) NC terminal should be open. Do not connect anything.

- (11) If the logic circuit power is off, do not apply the input signals.

- (12) Electro-Static Discharge Control, Since this module uses a CMOS LSI, the same careful attention should be paid to electrostatic discharge as for an ordinary CMOS IC. To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- Before remove LCM from its packing case or incorporating it into a set, be sure the module and your body have the same electric potential.Be sure to ground the body when handling the LCD modules.

- Tools required for assembling, such as soldering irons, must be properly grounded. make certain the AC power source for the soldering iron does not leak. When using an electric screwdriver to attach LCM, the screwdriver should be of ground potentiality to minimize as much as possible any transmission of electromagnetic waves produced sparks coming from the commutator of the motor.

- To reduce the amount of static electricity generated, do not conduct assembling and other work under dry conditions. To reduce the generation of static electricity be careful that the air in the work is not too dried. A relative humidity of 50%-60% is recommended. As far as possible make the electric potential of your work clothes and that of the work bench the ground potential.

The LCD module is coated with a film to protect the display surface. Exercise care when peeling off this protective film since static electricity may be generated.

- (13)Since LCM has been assembled and adjusted with a high degree of precision, avoid applying excessive shocks to the module or making any alterations or modifications to it.

- Do not alter, modify or change the shape of the tab on the metal frame.

- Do not make extra holes on the printed circuit board, modify its shape or change the positions of components to be attached.

- Do not damage or modify the pattern writing on the printed circuit board.

- Absolutely do not modify the zebra rubber strip (conductive rubber) or heat seal connector.

- Except for soldering the interface, do not make any alterations or modifications with a soldering iron.

- Do not drop, bend or twist LCM.

## 10.2 Storage Precautions

When storing the LCD modules, the following precaution is necessary.

- (1) Store them in a sealed polyethylene bag. If properly sealed, there is no need for the dessicant.

- (2) Store them in a dark place. Do not expose to sunlight or fluorescent light, keep the temperature between 0°C and 35°C.

- (3) The polarizer surface should not come in contact with any other objects. (We advise you to store them in the container in which they were shipped).

### 10.3 Others

Liquid crystals solidify under low temperature (below the storage temperature range) leading to defective orientation or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subject to a low temperature.

If the LCD modules have been operating for a long time showing the same display patterns, the display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. A normal operating status can be regained by suspending use for some time. It should be noted that this phenomenon does not adversely affect performance reliability.

To minimize the performance degradation of the LCD modules resulting from destruction caused by static electricity etc., exercise care to avoid holding the following

sections when handling the modules.

- Exposed area of the printed circuit board.

- Terminal electrode sections.

## 10.4 USING LCD MODULES Installing LCD Modules

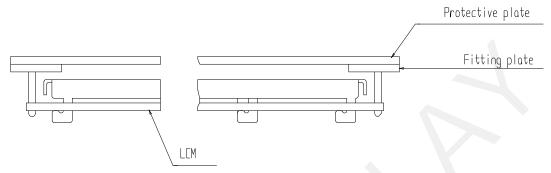

The hole in the printed circuit board is used to fix LCM as shown in the picture below. Attend to the following items when installing the LCM.

(1) Cover the surface with a transparent protective plate to protect the polarizer and LC cell.

(2) When assembling the LCM into other equipment, the spacer to the bit between the LCM and the fitting plate should have enough height to avoid causing stress to the module surface, refer to the individual specifications for measurements. The measurement tolerance should be  $\pm 0.1$ mm.

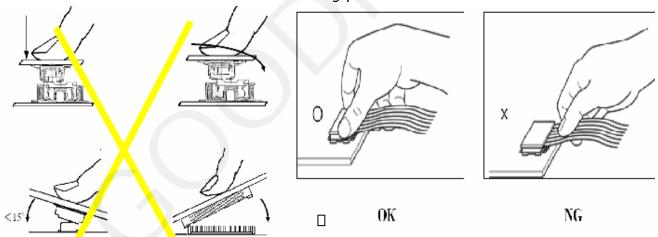

### Precaution for assemble the module with BTB connector:

Please note the position of the male and female connector position, don't assemble or assemble like the method which the following picture shows

### Precaution for soldering to the LCM

|                    | Hand soldering              | Machine drag                    | Machine press soldering          |

|--------------------|-----------------------------|---------------------------------|----------------------------------|

| No ROHS<br>Product | 290°C~350°C.<br>Time: 3-5S. | 330°C ~350°C.<br>Speed : 4-8mm/ | 300°C~330C.<br>Time: 3-6S.       |

|                    |                             | S.                              | Press: 0.8~1.2Mpa                |

| ROHS               | 340°C~370°C.                | 350°C ~370°C.                   | 330°C~360C.                      |

| Product            | Time : 3-5S.                | Time: 4-8 mm/s.                 | Time: 3-6S.<br>Press: 0.8~1.2Mpa |

(1)If soldering flux is used, be sure to remove any remaining flux after finishing to

soldering operation. (This does not apply in the case of a non-halogen type of flux.) It is recommended that you protect the LCD surface with a cover during soldering to prevent any damage due to flux spatters.

- (2) When soldering the electroluminescent panel and PC board, the panel and board should not be detached more than three times. This maximum number is determined by the temperature and time conditions mentioned above, though there may be some variance depending on the temperature of the soldering iron.

- (3) When remove the electroluminescent panel from the PC board, be sure the solder has completely melted, the soldered pad on the PC board could be damaged.

### **Precautions for Operation**

- (1) It is an indispensable condition to drive LCD's within the specified voltage limit since the higher voltage then the limit cause the shorter LCD life. An electrochemical reaction due to direct current causes LCD's undesirable deterioration, so that the use of direct current drive should be avoided.

- (2) Response time will be extremely delayed at lower temperature than the operating temperature range and on the other hand at higher temperature LCD's show dark color in them. However those phenomena do not mean malfunction or out of order with LCD's, Which will come back in the specified operating temperature.

- (3 If the display area is pushed hard during operation, the display will become abnormal. However, it will return to normal if it is turned off and then back on.

- (4) A slight dew depositing on terminals is a cause for electro-chemical reaction resulting in terminal open circuit. Usage under the maximum operating temperature,50%RH or less is required.

- (5) Input each signal after the positive/negative voltage becomes stable.

- (6) Please keep the temperature within specified range for use and storage. Polarization degradation, bubble generation or polarizer peel-off may occur with high temperature and high

#### Safety

humidity.

- (1) It is recommended to crush damaged or unnecessary LCDs into pieces and wash them off with solvents such as acetone and ethanol, which should later be burned.

- (2) If any liquid leaks out of a damaged glass cell and comes in contact with the hands, wash off thoroughly with soap and water.

- (3) WEEE order must be executed in product scrap.