# 6.0 inch E-paper Display Series

Dalian Good Display Co., Ltd.

# **Revision History**

| Rev. | Issued Date | Revised Contents                                                                            |  |  |  |

|------|-------------|---------------------------------------------------------------------------------------------|--|--|--|

| 1.0  | May.26.2020 | Preliminary                                                                                 |  |  |  |

| 1.1  | Jun.08.2020 | <ol> <li>In part 10: Modify Reliability test.</li> <li>In part 4: Modify module.</li> </ol> |  |  |  |

|      |             |                                                                                             |  |  |  |

# **TECHNICAL SPECIFICATION**

# **CONTENTS**

| NO. | ITEM                                          | PAGE |  |

|-----|-----------------------------------------------|------|--|

| -   | Cover                                         | 1    |  |

| -   | Revision History                              | 2    |  |

| -   | Contents                                      | 3    |  |

| 1   | Application                                   | 4    |  |

| 2   | Features                                      | 4    |  |

| 3   | Mechanical Specifications                     | 4    |  |

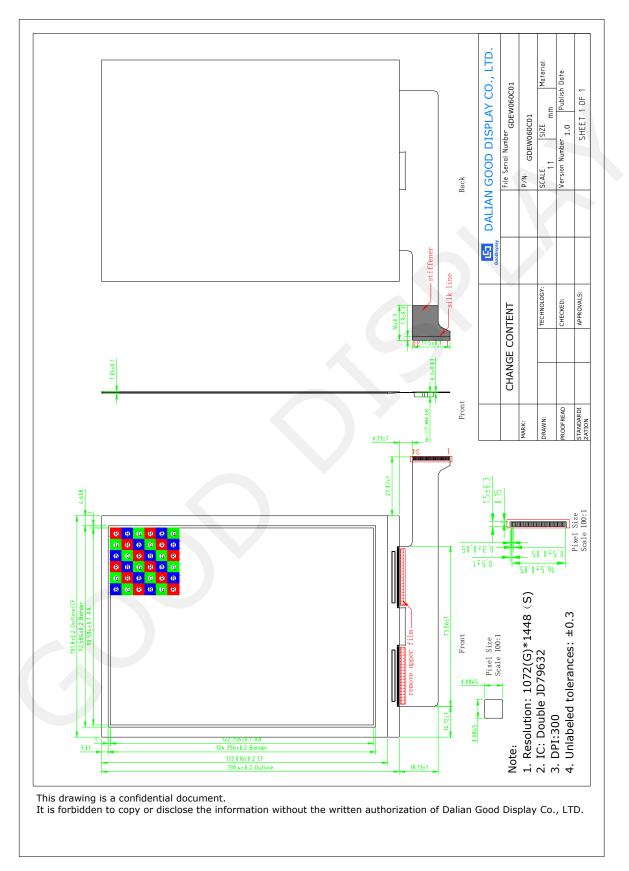

| 4   | Mechanical Drawing of DES module              | 5    |  |

| 5   | Input/Output Terminals                        | 6    |  |

| 6   | Electrical Characteristics                    | 7    |  |

| 7   | Power on sequence                             | 13   |  |

| 8   | Optical Characteristics                       | 15   |  |

| 9   | Handling, Safety and Environment Requirements | 17   |  |

| 10  | Reliability test                              | 18   |  |

| 11  | Point and line standard                       | 20   |  |

| 12  | Packing                                       | 21   |  |

#### 1. Over View

The display is a TFT active matrix electrophoretic display, with interface and a reference system design. The 6" active area contains  $1072 \times 1448$  pixels, and has 2-16 gray levels (1-4 bits) white/black full display capabilities.

#### 2. Features

- Carta high contrast reflective/electrophoretic technology

- 1072 x 1448 resolution

- Ultra wide viewing angle

- Low power consumption

- Pure reflective mode

- Bi-stable

- Commercial temperature range

- Landscape, portrait mode

## 3. Mechanical Specifications

| Parameter           | Specifications                  | Unit | Remark   |

|---------------------|---------------------------------|------|----------|

| Screen Size         | 6                               | Inch |          |

| Display Resolution  | play Resolution 1072(H)×1448(V) |      | Dpi: 300 |

| Active Area         | 90.584(H)×122.356(V)            | mm   |          |

| Pixel Pitch         | 0.0845×0.0845                   | mm   |          |

| Pixel Configuration | Square                          |      |          |

| Outline Dimension   | 101.8(H)×138.4(V) ×1.05(D)      | mm   |          |

| Weight              | $34.4 \pm 1$                    | g    |          |

# 5. Input/Output Terminals

# 5-1) Pin out List

| Pin # | Single | Description                         |  |

|-------|--------|-------------------------------------|--|

| 1     | VNEG   | Negative power supply source driver |  |

| 2     | VGL    | Negative power supply gate driver   |  |

| 3     | VSS    | Ground                              |  |

| 4     | NC     | No connection                       |  |

| 5     | NC     | No connection                       |  |

| 6     | VDD    | Digital power supply drivers        |  |

| 7     | VSS    | Ground                              |  |

| 8     | XCL    | Clock source driver                 |  |

| 9     | VSS    | Ground                              |  |

| 10    | XLE    | Latch enable source driver          |  |

| 11    | XOE    | Output enable source driver         |  |

| 12    | XSTL   | Start pulse gate driver             |  |

| 13    | D0     | Data signal source driver           |  |

| 14    | D1     | Data signal source driver           |  |

| 15    | D2     | Data signal source driver           |  |

| 16    | D3     | Data signal source driver           |  |

| 17    | D4     | Data signal source driver           |  |

| 18    | D5     | Data signal source driver           |  |

| 19    | D6     | Data signal source driver           |  |

| 20    | D7     | Data signal source driver           |  |

| 21    | VCOM   | Common connection                   |  |

| 22    | NC     | NO Connection                       |  |

| 23    | NC     | NO Connection                       |  |

| 24    | NC     | NO Connection                       |  |

| 25    | NC     | NO Connection                       |  |

| 26    | VSS    | Ground                              |  |

| 27    | MODE1  | Output mode selection gate driver   |  |

| 28    | CKV    | Clock gate driver                   |  |

| 29    | SPV    | Start pulse gate driver             |  |

| 30    | NC     | NO Connection                       |  |

| 31    | BORDER | Border connection                   |  |

| 32    | VSS    | Ground                              |  |

| 33    | VPOS   | Positive power supply source driver |  |

| 34    | VGH    | Positive power supply gate driver   |  |

# 6. Electrical Characteristics

## 6-1) Absolute maximum rating

| Parameter                | Symbol                | Rating        | Unit       |

|--------------------------|-----------------------|---------------|------------|

| Logic Supply Voltage     | VDD                   | -0.3 to +5    | V          |

| Positive Supply Voltage  | V <sub>POS</sub>      | -0.3 to +18   | V          |

| Negative Supply Voltage  | V <sub>NEG</sub>      | -0.3 to -18   | V          |

| Max .Drive Voltage Range | $V_{POS}$ - $V_{NEG}$ | 36            | V          |

| Supply Voltage           | VGG                   | -0.3 to +45   | V          |

| Supply Voltage           | VEE                   | -25.0 to +0.3 | V          |

| Supply Range             | VGG-VEE               | -0.3 to +45   | V          |

| Operating Temp. range    | T <sub>OPR</sub>      | -10 to +60    | $^{\circ}$ |

| Storage Temp. range      | T <sub>STG</sub>      | -25 to +75    | °C         |

## 6-2) Panel DC Characteristics

| Parameter              | Symbol                  | Conditions          | Min   | Тур      | Max    | Unit |

|------------------------|-------------------------|---------------------|-------|----------|--------|------|

| Single ground          | V <sub>SS</sub>         |                     | - /   | 0        | -      | V    |

| Lasia Sumply Valtage   | V <sub>DD</sub>         |                     | 1.7   | 3.0      | 3.6    | V    |

| Logic Supply Voltage   | I <sub>VDD</sub>        | $V_{DD}=3.0V$       | -     | 3.1      | 7.8    | mA   |

| Cata Nagating Supply   | VGL                     |                     | -20   | -        | VNEG-4 | V    |

| Gate Negative Supply   | I <sub>GL</sub>         | VGL=-20V            | -     | 1.2      | 12     | mA   |

| Cata Dagitiya Supply   | VGH                     |                     | 7     | VGL+42   | VGL+45 | V    |

| Gate Positive Supply   | I <sub>GH</sub>         | VGH=22V             | -     | 1.2      | 2.5    | mA   |

| Source Negative Supply | <b>V</b> <sub>NEG</sub> |                     | -15.4 | -        | -10    | V    |

| Source Negative Supply | I <sub>NEG</sub>        | $V_{NEG} = -15V$    | -     | 8.5      | 160    | mA   |

| Source Desitive Supply | V <sub>POS</sub>        |                     | 10    | -        | 15     | V    |

| Source Positive Supply | I <sub>POS</sub>        | $V_{POS} = 15 V$    | -     | 8.2      | 166    | mA   |

| Border Supply          | V <sub>com</sub>        |                     | -4    | Adjusted | -0.2   | V    |

| Asymmetry Source       | V <sub>ASYM</sub>       | $V_{POS} + V_{NEG}$ | -800  | 0        | 800    | mV   |

| Common voltooo         | V <sub>COM</sub>        |                     | -4    | Adjusted | -0.2   | V    |

| Common voltage         | I <sub>COM</sub>        |                     | -     | 0.2      | -      | mA   |

| Panel Power            | Р                       |                     | -     | 285      | 4680   | mW   |

| Standby power panel    | P <sub>STBY</sub>       |                     | -     | -        | 1.3    | mW   |

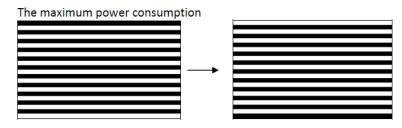

- The maximum power consumption is measured using 85 Hz waveform with following pattern transition: from pattern of repeated 1 consecutive black scan lines followed by 1 consecutive white scan line to that of repeated 1 consecutive white scan lines followed by 1 consecutive black scan lines. (Note 1)

- The Typical power consumption is measured using 85 Hz waveform with following pattern transition: from horizontal

4 gray scale pattern to vertical 4 gray scale pattern. (Note 2)

- The standby power is the consumed power when the panel controller is in standby mode.

- The listed electrical/optical characteristics are only guaranteed under the controller & waveform provided by Good

Display.

- Vcom is recommended to be set in the range of assigned value  $~\pm~~0.1~V$

- The maximum  $I_{\text{COM}}$  inrush current is about 1000 mA

- Customer need to use decoupling capacitors on each power rail at system board as below table to keep EPD driving power stable. (Note 3)

Note 1

The maximum power consumption

Note 2

Note 3

The decoupling capacitors on each power rail at customer system side

| Power rail | Capacitors suggested ( uF / Tolerance)          |

|------------|-------------------------------------------------|

| IPOS       | $4.7 \mathrm{uF} \ge 2 \mathrm{pcs} / \pm 10\%$ |

| INEG       | 4.7uF x 2pcs / $\pm 10\%$                       |

| IGH        | 4.7uF x 1pcs / $\pm 10\%$                       |

| IGL        | $4.7 \mathrm{uF \ x \ 1pcs} \ / \ \pm 10\%$     |

| IDD        | $4.7 \text{uF x } 1 \text{pcs} / \pm 10\%$      |

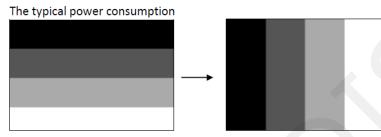

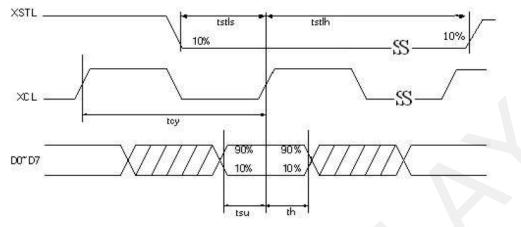

# **6-3) Panel AC Characteristics**

VDD=3.0V, unless otherwise specified.

| Parameter                                             | Symbol | Min.    | Тур. | Max.    | unit |

|-------------------------------------------------------|--------|---------|------|---------|------|

| Clock frequency                                       | fckv   | -       | -    | 200     | kHz  |

| Minimum "L" clock pulse width                         | twL    | 1       | -    | -       | us   |

| Minimum "H" clock pulse width                         | twH    | 1       | -    | -       | us   |

| Clock rise time                                       | trckv  | -       | -    | 100     | ns   |

| Clock fall time                                       | tfckv  | -       | -    | 100     | ns   |

| SPV setup time                                        | tSU    | 100     | -    | twH-100 | ns   |

| SPV hold time                                         | tH     | 100     | -    | twH-100 | ns   |

| Pulse rise time                                       | trspv  | -       | -    | 100     | ns   |

| Pulse fall time                                       | tfspv  | -       | -    | 100     | ns   |

| Clock XCL cycle time                                  | tcy    | 22.22   | -    |         | ns   |

| D0D7setup time                                        | tsu    | 11      | -    | -       | ns   |

| D0D7 hold time                                        | th     | 11      | -    | -       | ns   |

| XSTL setup time                                       | tstls  | 0.5*tcy | -    | 0.8*tcy | ns   |

| XSTL hold time                                        | tstlh  | 0.5*tcy | -    | -       | ns   |

| XLE on delay time                                     | tLEdly | 4.5*tcy | -    | -       | ns   |

| LEH high-level pulse width<br>(When VDD=1.7V to 2.1V) | tLEW   | 400     | -    | -       | ns   |

| XLE off delay time                                    | tLEoff | 250     | -    | -       | ns   |

| Output setting time to +/-30mV<br>(C load=200pF)      | tout   | -       | -    | 20      | us   |

# **CLOCK & DATA TIMING**

Note 1: First gate line on timing . After 5 CKV, gate line be on.

# 6-4) Refresh rate

The module applied at a maximum refresh rate of 85 Hz.

|              | Min | Max  |

|--------------|-----|------|

| Refresh rate | -   | 85Hz |

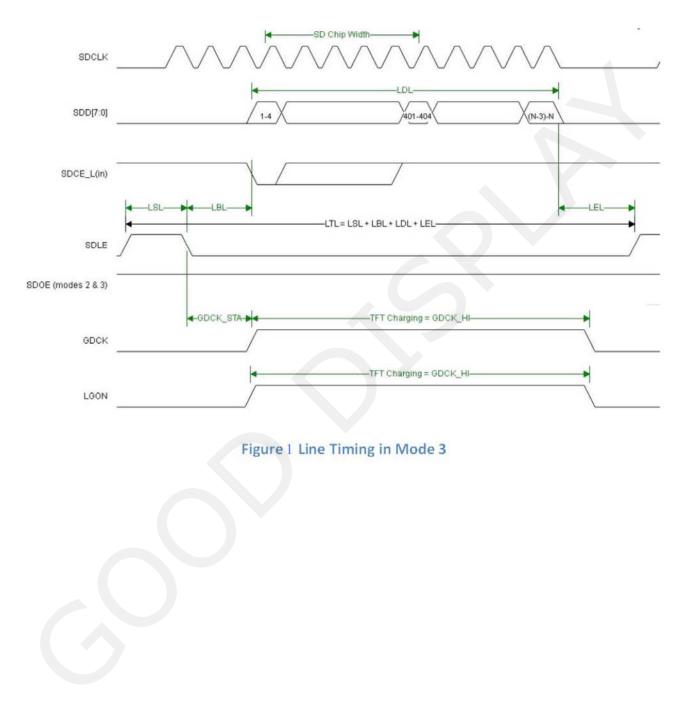

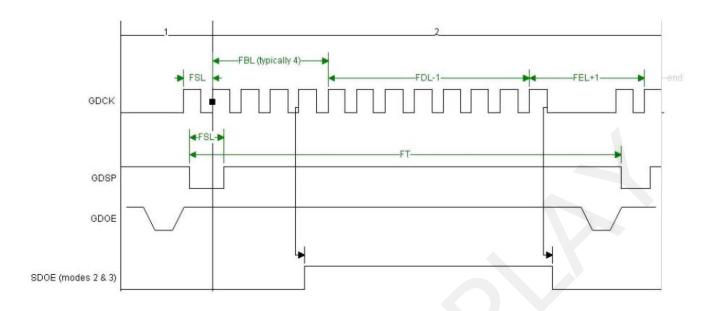

# **6-5) Controller Timing**

This timing mode is depicted on Figure 1 and Figure 2 and it refers to timing of Source Driver Output Enable (SDOE) and Gate Driver Clock (GDCK). Note, that in this mode LGON follows GDCK timing.

| Mode             | 3     |      |       |      |          |        |

|------------------|-------|------|-------|------|----------|--------|

| SDCK(MHz)        | 40    |      |       |      |          |        |

| Pixel per SDCK   | 4     |      |       |      |          |        |

| Line Parameters  | LSL   | LBL  | LDL   | LEL  | GDCK_STA | LGONL  |

| (SDCK)           | 14    | 8    | 362   | 51   | 100      | 281    |

| Line Parameters  | -     | -    | -     | -    | -        | -      |

| (us)             | 0.35  | 0.20 | 9.05  | 1.28 | 2.5      | 7.03   |

| Frame parameters | FSL   | FBL  | FDL   | FEL  | -        | FR(Hz) |

| (lines)          | 2     | 4    | 1072  | 4    | -        | 84.99  |

| Frame parameters |       |      |       |      | -        | -      |

| (us)             | 21.75 | 43.5 | 11658 | 43.5 | _        | -      |

Note 1 : For parameters definition, see Section 6. Active Matrix Electronic Paper Display Timings

Note 2 : For Isis Controller GDCK\_STA and LGONL are not settable parameters ; GDCK\_STA=LBL, LGONL=LDL+0.5

Note 3 : For Freescale SoC GDOE Low pulse represent FSL and GDSP pulses with the first period of FBL Note 4 :

SDCLK = XCL SDD[7:0] = D0~D7  $SDCE_L(in) = XSTL$  GDCK = CKV GDSP = SPV GDOE = Mode 1SDOE = XOE

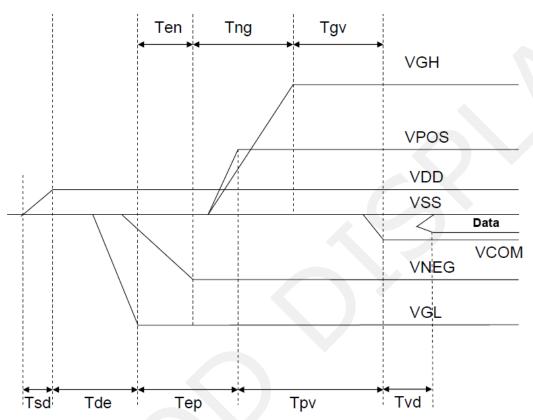

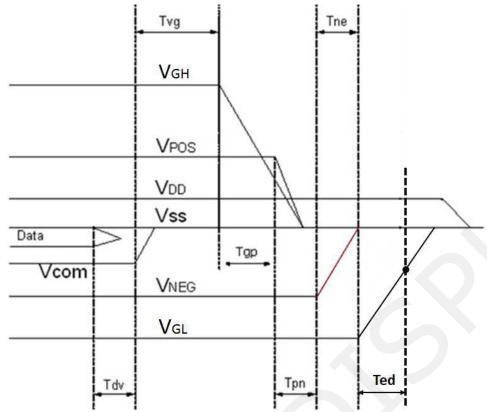

# 7. Power on sequence

Power Rails must be sequenced in following order:

- 1.  $VSS \rightarrow VDD \rightarrow VNEG \rightarrow VPOS$  (Source driver)  $\rightarrow VCOM$

- 2.  $VSS \rightarrow VDD \rightarrow VGL \rightarrow VGH(Gate drive)$

POWER ON

|     | Min    | Max |

|-----|--------|-----|

| Tsd | 30us   | -   |

| Tde | 100us  | -   |

| Тер | 1000us | -   |

| Tpv | 100us  | -   |

| Tvd | 100us  | -   |

| Ten | Ous    | -   |

| Tng | 1000us | -   |

| Tgv | 100us  | -   |

Power OFF

|     | Min   | Max | Remark                       |

|-----|-------|-----|------------------------------|

| Tdv | 100us | -   | -                            |

| Tvg | Ous   | -   | -                            |

| Tgp | Ous   | -   | -                            |

| Tpn | Ous   | -   | -                            |

| Tne | Ous   | -   | -                            |

| Ted | 0.5s  | -   | Discharged point @ -7.4 Volt |

Note 1: Supply voltages decay through pull-down resistors.

Note 2: Turn off VGL power after VNEG and VPOS power discharged to GND state.

Note 3: VGL must remain negative of Vcom during decay period.

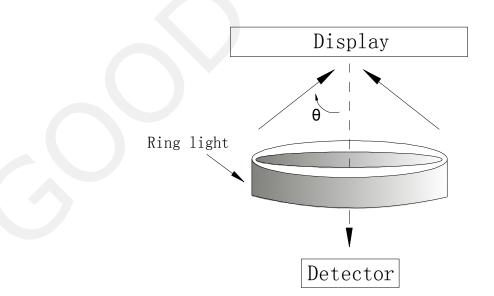

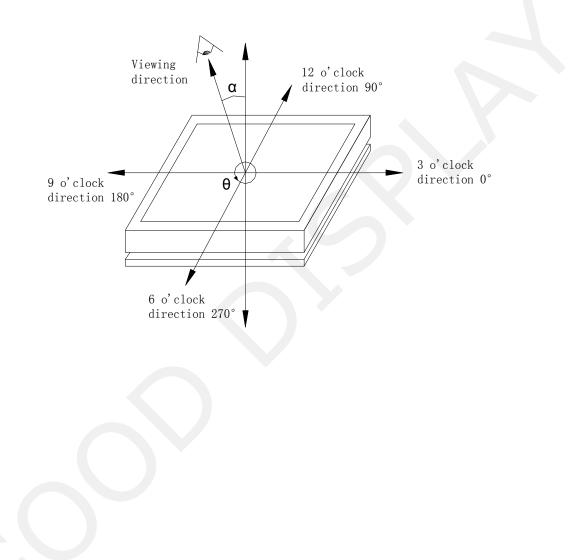

## 8. Optical characteristics

#### 8-1) Specifications

Measurements are made with that the illumination is under an angle of 45 degrees, the detection is perpendicular unless otherwise specified.

|                     |                |            |     |                             |     | T=25°C |          |

|---------------------|----------------|------------|-----|-----------------------------|-----|--------|----------|

| SYMBOL              | PARAMETER      | CONDITIONS | MIN | ТҮРЕ                        | MAX | UNIT   | Note     |

| R                   | Reflectance    | White      | 30  | 35                          | -   | %      | Note 8-1 |

| Gn                  | Nth Grey Level | -          | -   | $DS+(WS-DS) \times n/(m-1)$ | -   | L*     | -        |

| CR                  | Contrast Ratio | indoor     | 8   |                             |     | -      | -        |

| T <sub>update</sub> | Update time    | 25℃        | -   | 1                           | -   | Sec    | -        |

| Panel's life        |                | -10°C~60°C |     | 1000000 times or 5 years    | -   | -      | Note 8-2 |

WS : White state; DS : Dark state, Gray state from Dark to White : DS, G1, G2..., Gn..., Gm-2, WS

m: 4, 8, 16 when 2, 3, 4 bit mode.

Note 8-1: Luminance meter: Eye - One Pro Spectrophotometer

Note 8-2: Each update interval time should be minimum at 180 seconds.

Note 8-3: When work in temperature 60 degree, suggest update once every 1hours.

#### 9-2) Definition of contrast ratio

The contrast ratio (CR) is the ratio between the reflectance in a full white area (R1) and the reflectance in a dark area (Rd)() :

R1: white reflectance Rd: dark reflectance

CR = R1/Rd

GDEW060C01

#### 8-3) Reflection Ratio

The reflection ratio is expressed as :

$R = Reflectance \; Factor \;_{white \; board} \quad x \; (L_{\; center} \; / \; L_{\; white \; board} \; )$

$L_{center}$  is the luminance measured at center in a white area (R=G =B=1) .  $L_{white board}$  is the luminance of a standard white board. Both are measured with equivalent illumination source. The viewing angle shall be no more than 2 degrees.

#### 9. Handling, Safety and Environmental Requirements

#### Warning

The display glass may break when it is dropped or bumped on a hard surface. Handle with care.

Should the display break, do not touch the electrophoretic material. In case of contact with electrophoretic material, wash with water and soap.

Caution

The display module should not be exposed to harmful gases, such as acid and alkali gases, which corrode electronic components. Disassembling the display module can cause permanent damage and invalidate the warranty agreements.

Observe general precautions that are common to handling delicate electronic components. The glass can break and front surfaces can easily be damaged. Moreover the display is sensitive to static electricity and other rough environmental conditions.

| Data sheet status                                                                                                                   |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Product specification The data sheet contains final product specifications.                                                         |  |  |  |  |

| Limiting values                                                                                                                     |  |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134).                                          |  |  |  |  |

| Stress above one or more of the limiting values may cause permanent damage to the device.                                           |  |  |  |  |

| These are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics |  |  |  |  |

| sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.       |  |  |  |  |

| Application information                                                                                                             |  |  |  |  |

| Where application information is given, it is advisory and dose not form part of the specification.                                 |  |  |  |  |

|      | Product environmental certification |

|------|-------------------------------------|

| RoHS |                                     |

# 10. Reliability test

|   | TEST                                                   | CONDITION                                                       | METHOD                                                                                                                                                                                                                                                                                                                             | REMARK                                                                                                   |

|---|--------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|   |                                                        |                                                                 | When the experimental cycle finished, the DES samples                                                                                                                                                                                                                                                                              | When experiment                                                                                          |

| 1 | High-Temperatu<br>re Operation                         | T = 60°C,<br>RH=20%<br>for 240 hrs                              | will be taken out from the high<br>temperature environmental chamber and set aside for a few<br>minutes. As DESs return to room temperature, testers will<br>observe the appearance, and test electrical and optical<br>performance based on standard # IEC 60 068-2-2Bp.                                                          | finished, the DES<br>must meet electrical<br>and optical<br>performance<br>standards.                    |

| 2 | Low-Temperatu re Operation                             | T = -10°C for 240<br>hrs                                        | When the experimental cycle finished, the DES samples<br>will be taken out from the low<br>temperature environmental chamber and set aside for a few<br>minutes. As DESs return room temperature, testers will<br>observe the appearance, and test electrical and optical<br>performance based on standard # IEC 60 068-2-2Ab.     | When experiment<br>finished, the DES<br>must meet electrical<br>and optical<br>performance<br>standards. |

| 3 | High-Temperatu<br>re Storage                           | T = +70°C,<br>RH=20%<br>for 240 hrs<br>Test in white<br>pattern | When the experimental cycle finished, the DES samples<br>will be taken out from the high<br>temperature environmental chamber and set aside for a few<br>minutes. As DESs return to room temperature, testers will<br>observe the appearance, and test electrical and optical<br>performance based on standard # IEC 60 068-2-2Bp. | When experiment<br>finished, the DES<br>must meet electrical<br>and optical<br>performance<br>standards. |

| 4 | Low-Temperatu<br>re Storage                            | T = -25°C for 240<br>hrs<br>Test in white<br>pattern            | When the experimental cycle finished, the DES samples<br>will be taken out from the low<br>temperature environmental chamber and set aside for a few<br>minutes. As DESs return to room temperature, testers will<br>observe the appearance, and test electrical and optical<br>performance based on standard # IEC 60 068-2-2Ab   | When experiment<br>finished, the DES<br>must meet electrical<br>and optical<br>performance<br>standards. |

| 5 | High<br>Temperature,<br>High-<br>Humidity<br>Operation | T=+40°C,<br>RH=90%<br>for240hrs                                 | When the experimental cycle finished, the DES samples<br>will be taken out from the environmental chamber and set<br>aside for a few minutes. As DESs return to room<br>temperature, testers will observe the appearance, and test<br>electrical and optical performance based on standard # IEC<br>60 068-2-3CA.                  | When experiment<br>finished, the DES<br>must meet electrical<br>and optical<br>performance<br>standards. |

| 6 | High<br>Temperature,<br>High-<br>Humidity<br>Storage   | T=+60°C,<br>RH=80%<br>for 240 hrs<br>Test in white<br>pattern   | When the experimental cycle finished, the DES samples will be taken out from the environmental chamber and set aside for a few minutes. As DESs return to room temperature, testers will observe the appearance, and test electrical and optical performance based on standard # IEC 60 068-2-3CA.                                 | When experiment<br>finished, the DES<br>must meet electrical<br>performance<br>standards.                |

| 7 | Temperature<br>Cycle                                   | [-25°C 30mins]→<br>[+70°C, RH=20%<br>30mins],                   | <ol> <li>Samples are put in the Temp &amp; Humid. Environmental<br/>Chamber. Temperature cycle starts with -25°C, storage<br/>period 30 minutes. After 30 minutes, it needs 30min to</li> </ol>                                                                                                                                    | When experiment<br>finished, the DES<br>must meet electrical                                             |

|                        |                            | 70cycles,                            | let temperature rise to 75°C. After 30min, temperature    | and optical |

|------------------------|----------------------------|--------------------------------------|-----------------------------------------------------------|-------------|

| Test in whi<br>pattern |                            | Test in white                        | will be adjusted to 75°C, RH=20% and storage period       | performance |

|                        |                            | pattern                              | is 30 minutes. After 30 minutes, it needs 30min to let    | standards.  |

|                        |                            |                                      | temperature rise to -25°C. One temperature cycle          |             |

|                        |                            |                                      | (2hrs) is complete.                                       |             |

|                        |                            |                                      | 2. Temperature cycle repeats 70 times.                    | 4           |

|                        |                            |                                      | 3. When 70 cycles finished, the samples will be taken out |             |

|                        |                            |                                      | from experiment chamber and set aside a few minutes.      |             |

|                        |                            |                                      | As DESs return to room temperature, tests will            |             |

|                        |                            |                                      | observe the appearance, and test electrical and optical   |             |

|                        |                            |                                      | performance based on standard # IEC 60 068-2-14NB.        |             |

| 0                      | UV exposure                | $765 \text{ W/m}^2 \text{ for } 168$ | Standard # IEC 60 068-2-5 Sa                              |             |

| 8                      | Resistance                 | hrs,40°C                             | Standard # IEC 60 068-2-5 Sa                              |             |

|                        | Electrostatic<br>discharge | Machine model:                       |                                                           |             |

| 9                      |                            | +/-250V,                             | Standard # IEC61000-4-2                                   |             |

|                        |                            | 0 Ω ,200pF                           |                                                           |             |

|                        | Package<br>Vibration       | 1.04G,Frequency :                    |                                                           |             |

|                        |                            | 10~500Hz                             |                                                           |             |

| 10                     |                            | Direction : X,Y,Z                    | Full packed for shipment                                  |             |

|                        |                            | Duration:1hours                      |                                                           |             |

|                        |                            | in each direction                    |                                                           |             |

|                        | Package Drop<br>Impact     | Drop from height                     |                                                           |             |

| 11                     |                            | of 122 cm on                         |                                                           |             |

|                        |                            | Concrete surface                     |                                                           |             |

|                        |                            | Drop sequence:1                      | Full packed for shipment                                  |             |

|                        |                            | corner, 3edges,                      | run packed for sinpilient                                 |             |

|                        |                            | 6face                                |                                                           |             |

|                        |                            | One drop for                         |                                                           |             |

|                        |                            | each.                                |                                                           |             |

Actual EMC level to be measured on customer application.

Note: (1) The protective film must be removed before temperature test.

(2) In order to make sure the display module can provide the best display quality, the update should be made after putting the display module in stable temperature environment for 4 hours at 25 °C.

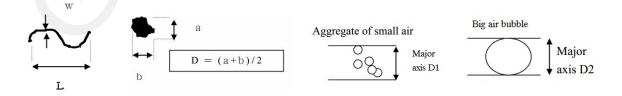

#### 11. Point and line standard

#### **Shipment Inseption Standard**

Part-A: Active area Part-B: Border area

Equipment: Electrical test fixture, Point gauge

Outline dimension:

| $101.8(H)\!\!\times\!\!138.4(V)\times\!\!1.05(D)$ | Unit: mm                                             |                                                    |             |                                                             |        |        |  |

|---------------------------------------------------|------------------------------------------------------|----------------------------------------------------|-------------|-------------------------------------------------------------|--------|--------|--|

|                                                   | Temperature                                          | Humidity                                           | Illuminan   | ce Distance                                                 | Time   | Angle  |  |

| Environment                                       | 23±2°C                                               | $55\pm$                                            | $1200 \sim$ | 300 mm                                                      | 35 Sec |        |  |

|                                                   |                                                      | 5%RH                                               | 1500Lux     |                                                             | 55 500 |        |  |

| Name                                              | Causes                                               | Spot size                                          |             | Part-A                                                      | Part-B |        |  |

|                                                   | D/W spot in alass on                                 |                                                    | $D \leq 0.$ | Ignore                                                      |        |        |  |

| Smot                                              | B/W spot in glass or                                 | $0.25$ mm $<$ D $\leq$ 0.4mm                       |             |                                                             | 4      | Ignore |  |

| Spot                                              | protection sheet,<br>foreign mat. Pin hole           | $0.4$ mm $< D \leq 0.5$ mm                         |             |                                                             | 2      |        |  |

|                                                   | Toreign mat. Fin noie                                |                                                    | 0.5mm       | 0                                                           |        |        |  |

|                                                   | Scratch on glass or                                  | Length                                             |             | Width                                                       | Part-A |        |  |

| Scratch or line defect                            | Scratch on FPL or                                    | $L \leq 3mm$                                       |             | W≤0.1 mm                                                    | Ignore | Ianana |  |

| Scratch of the defect                             | Particle is Protection                               | 3 mm < L                                           | ≤ 6mm       | 0.1 mm <w≤ 0.2mm<="" td=""><td>1 2</td><td>Ignore</td></w≤> | 1 2    | Ignore |  |

|                                                   | sheet.                                               | 6 mm                                               | < L         | 0.2mm < W                                                   | 0      |        |  |

|                                                   |                                                      | D1, D2 $\leq$ 0.3 mm                               |             |                                                             | Ignore | Ignore |  |

| Air bubble                                        | Air bubble                                           | $0.3 \text{ mm} < \text{D1,D2} \leq 0.5 \text{mm}$ |             |                                                             | 4      |        |  |

|                                                   |                                                      | 0.5mm < D1, D2                                     |             |                                                             | 0      |        |  |

| Side Fragment                                     |                                                      |                                                    | x<br>y y    |                                                             |        |        |  |

|                                                   | $X \leq 6$ mm, $Y \leq 1$ mm & display is ok, Ignore |                                                    |             |                                                             |        |        |  |

Remarks: Spot define: That only can be seen under WS or DS defects.

Any defect which is visible under gray pattern or transition process but invisible under black and white is disregarded.

Here is definition of the "Spot" and "Scratch or line defect".

Spot: W > 1/4LScratch or line defect: W  $\leq 1/4L$

Definition for L/W and D (major axis)

FPC bonding area pad doesn't allowed visual inspection.

Note: AQL = 0.4

**12. Packing** TBD